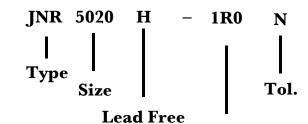

### **PRODUCT IDENTIFICATION**

### **FEATURES**

- 1. This specification applies Low Profile Power Inductors.

- 2. 100% Lead(Pb) & Halogen-Free and RoHS compliant.

3. Operating temperature :-40~+125° (Including self temperature rise)

## **Inductance**

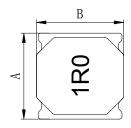

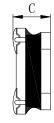

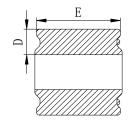

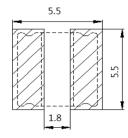

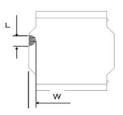

## **DIMENSIONS (mm)**

| Part No.  | Size (mm)     |               |           |           |               |  |  |

|-----------|---------------|---------------|-----------|-----------|---------------|--|--|

| Fait NO.  | Α             | В             | С         | D         | Е             |  |  |

| JNR 5020H | $5.0 \pm 0.2$ | $5.0 \pm 0.2$ | 1.6 ± 0.2 | 1.8 ± 0.2 | $4.7 \pm 0.2$ |  |  |

<sup>\*</sup> Dimensions are not including the termination.

For maximum overall dimensions with termination, add 0.1mm.

#### **Recommended PC Board Pattern**

### Note:

- 1. The above PCB layout reference only.

- 2. Recommend solder paste thickness at

- 0.12mm and above.

### SERIES LIST

|     |                | L          | Tol. | RDC           | Isat | Irms |

|-----|----------------|------------|------|---------------|------|------|

| No. | Part No.       |            |      | (m $\Omega$ ) | (A)  | (A)  |

|     |                | ( $\mu$ H) |      | ±20%          |      |      |

| 1   | JNR 5020H-1R0N | 1.0        | ±30% | 20            | 5.00 | 4.10 |

| 2   | JNR 5020H-1R2N | 1.2        | ±30% | 20            | 4.80 | 3.80 |

| 3   | JNR 5020H-1R5N | 1.5        | ±30% | 25            | 4.50 | 3.50 |

| 4   | JNR 5020H-2R2M | 2.2        | ±20% | 32            | 4.10 | 3.30 |

| 5   | JNR 5020H-2R7M | 2.7        | ±20% | 38            | 3.80 | 3.00 |

| 6   | JNR 5020H-3R3M | 3.3        | ±20% | 43            | 3.50 | 2.80 |

| 7   | JNR 5020H-4R7M | 4.7        | ±20% | 60            | 2.70 | 2.40 |

| 8   | JNR 5020H-5R6M | 5.6        | ±20% | 69            | 2.40 | 2.10 |

| 9   | JNR 5020H-6R8M | 6.8        | ±20% | 90            | 2.10 | 1.90 |

| 10  | JNR 5020H-8R2M | 8.2        | ±20% | 98            | 1.90 | 1.75 |

| 11  | JNR 5020H-100M | 10         | ±20% | 110           | 1.70 | 1.60 |

| 12  | JNR 5020H-120M | 12         | ±20% | 135           | 1.40 | 1.40 |

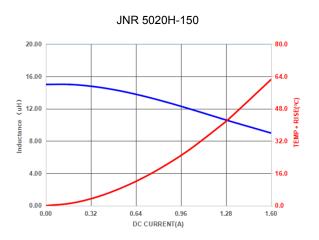

| 13  | JNR 5020H-150M | 15         | ±20% | 165           | 1.30 | 1.25 |

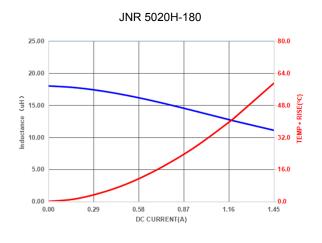

| 14  | JNR 5020H-180M | 18         | ±20% | 190           | 1.20 | 1.17 |

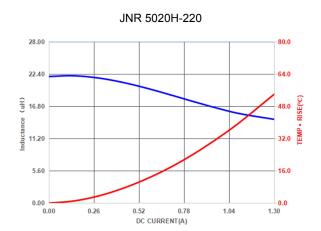

| 15  | JNR 5020H-220M | 22         | ±20% | 225           | 1.10 | 1.10 |

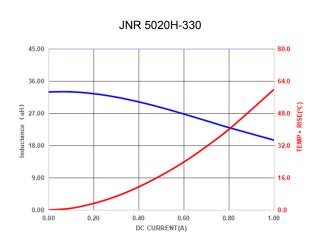

| 16  | JNR 5020H-330M | 33         | ±20% | 335           | 0.80 | 0.80 |

| 17  | JNR 5020H-470M | 47         | ±20% | 460           | 0.70 | 0.70 |

#### Note:

1. Test Frequency: 100KHz /1V

2. All test data referenced to 25°C ambient

3. Isat: Saturation Current (Isat) will cause L0 to drop approximately 30%.

4. Irms : Heat Rated Current (Irms) will cause the coil temperature rise approximately  $\Delta T$  of  $40^\circ\!\!\!\! \text{C}$

- 5. The part temperature (ambient + temp rise) should not exceed 125°C under worst case operating conditions. Circuit design,component,PCB trace size and thickness,airflow and other cooling provisions all affect the part temperature. Part temperature should be verified in the end application.

- 6. Special inquiries besides the above common used types can be met on your requirement.

- 7. Rated DC current: The lower value of Irms and Isat.

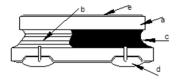

### Materials

| No. | Description | Specification              |  |  |

|-----|-------------|----------------------------|--|--|

| а   | Core        | Ferrite Core               |  |  |

| b   | Wire        | Enameled Copper Wire       |  |  |

| С   | Glue        | Epoxy with magnetic powder |  |  |

| d   | Terminal    | Ag/Ni/Sn+ Sn Solder        |  |  |

| е   | lnk         | Halogen-free ketone        |  |  |

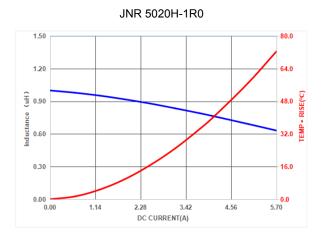

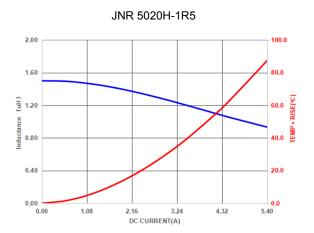

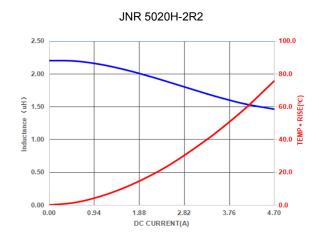

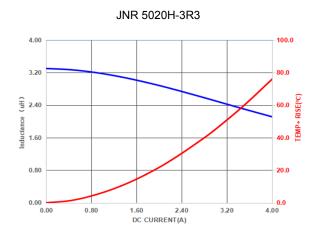

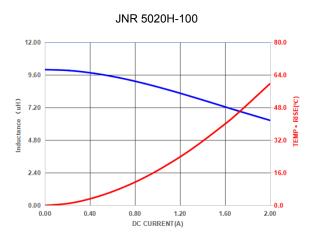

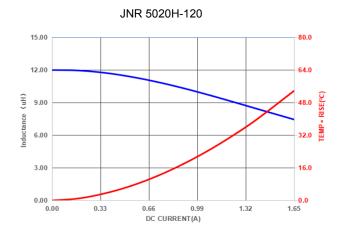

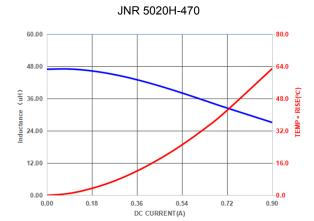

# **■ TYPICAL PERFORMANCE CURVES**

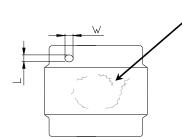

### Appearance criterion

#### 1 . Core chipping

The appearance standard of the chipping size on top side, and bottom side ferrite core is listed below.

Chip off is generated during molding and manufacturing process.

Chip off acceptance limits subjected to the product size.

Our current Defect limit is based on the IPC-A-610.

Some chip off does not impact the product function, see the IPC standard 1 & 2.

| L | ≤50 % of the length |

|---|---------------------|

| W | ≤25 % of the width  |

Defects usually occur at the corners and edges of the product,

There will be a slight defect black and rough, but not exposed copper, and does not affect the product performance and reliability.

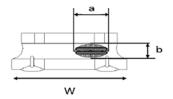

#### 2 . Void appearance tolerance Limit

Size of voids occurring to coating resin is specified below.

Exposed wire tolerance limit of coating resin part on product side. Size of exposed wire occurring to coating resin is specified below.

- 1. Width direction (dimension a) : Acceptable when  $a \le w/2$ .

- 2. Length direction (dimension b): Dimension b is not specified.

- 3. The total area of exposed wire occurring to each sides is not greater than 50% of coating resin area, and is acceptable.

#### 3 . External appearance criterion for exposed wire

Exposed winding wire at the secondary side is regarded as qualified product.

#### 4. Electrode appearance criterion for exposed wire

. Visual check on core surface with no crack means pass.

Only top side of wire is exposed. (regardless of whole tope side of wire exposed)

Conforming

$\sim\sim$

Less than 1/2 of joint side length. (More than 1/2 is selected as defect)

Wire is soldered insufficiently and less than half of outer diameter is covered with solder.

L & W

≤20% of the area on one single pad

Foreign materials on the product body is inevitable and accepted.

Electrodes with foreign body (dirt) appearance standards

Foreign materials (dirt) will not affect the coplanarity of PAD,

below the example of foreign materials (dirt) quantity  $\leq$ 2PCS on single PAD.

Dimensions range as shown in the table.

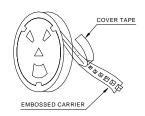

# **Packaging Information**

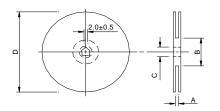

# • Reel Dimension

| Туре     | A(mm)    | B(mm)  | C(mm)       | D(mm)   |

|----------|----------|--------|-------------|---------|

| 13"x12mm | 13.4+2-0 | 80±2.0 | 13+0.5/-0.2 | 330±3.0 |

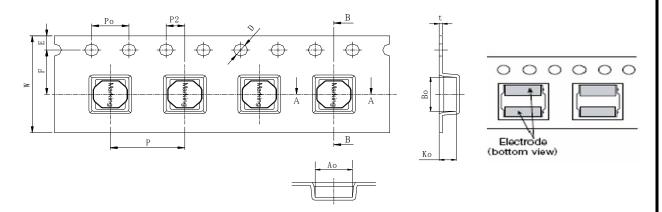

# • Tape Dimension

| Ao(mm)  | Bo(mm)  | Ko(mm)  | P(mm)   | w(mm)  | t(mm)   | Emm)     | F(mm)   | D(mm)   | Po(mm)  | P2(mm)   |

|---------|---------|---------|---------|--------|---------|----------|---------|---------|---------|----------|

| 5.4±0.1 | 5.4±0.1 | 2.2±0.1 | 8.0±0.1 | 12±0.3 | 0.4±0.1 | 1.75±0.1 | 7.5±0.1 | 1.5±0.1 | 4.0±0.1 | 2.00±0.1 |

# • Packaging Quantity

| Size      | Reel |

|-----------|------|

| JNR 5020H | 2500 |

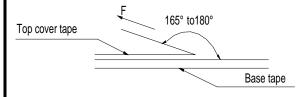

# • Tearing Off Force

The force for tearing off cover tape is 10 to 130 grams in the arrow direction under the following conditions (referenced ANSI/EIA-481-D-2008 of 4.11 standard).

| Tearing Speed | Room Temp. | Room Humidity | Room atm |

|---------------|------------|---------------|----------|

| mm            | (℃)        | (%)           | (hPa)    |

| 300±10%       | 5~35       | 45~85         | 860~1060 |

# Application Notice

Storage Conditions(component level)

To maintain the solderability of terminal electrodes:

- 1. Products meet IPC/JEDEC J-STD-020E standard-MSL, level 1.

- 2. Temperature and humidity conditions: Less than  $40^\circ\!\!\!\!\mathrm{C}$  and 60% RH.

- 3. Recommended products should be used within 12 months form the time of delivery.

- 4. The packaging material should be kept where no chlorine or sulfur exists in the air.

- Transportation

- 1. Products should be handled with care to avoid damage or contamination from perspiration and skin oils.

- 2. The use of tweezers or vacuum pick up is strongly recommended for individual components.

- 3. Bulk handling should ensure that abrasion and mechanical shock are minimized.