### **FEATURES**

- 1. Low loss realized with low DCR.

- 2. High performance realized by metal dust core.

- 3. Ultra low buzz noise, due to composite construction.

- 4. 100% Lead(Pb)-Free and RoHS compliant.

Inductance

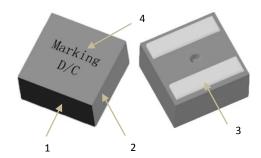

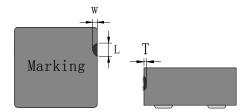

## **■** Marking and Date code:

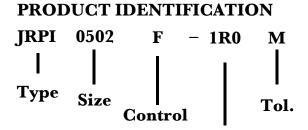

Marking ex:1.0( $\mu$ H)  $\rightarrow$  1R0

# Date code 21 12 → year and weekly

## **APPLICATIONS**

Commercial applications

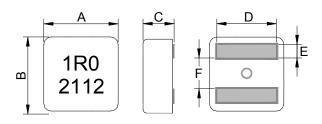

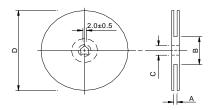

## **DIMENSIONS (mm)**

**RDC Test**

Marking: Black.1R0 and 2112 (21 YY,12 WW,follow production date)

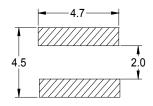

#### **Recommend PC Board Pattern**

#### Note:

- 1. PCB layout is referred to standard IPC-7351B

- 2. The above PCB layout reference only.

- 3. Recommend solder paste thickness at 0.12mm and above.

| Part No.   | Size (mm) |           |           |               |           |            |  |  |

|------------|-----------|-----------|-----------|---------------|-----------|------------|--|--|

| Part No.   | Α         | В         | С         | D             | E         | F          |  |  |

| JRPI 0502F | 6.0 ± 0.2 | 5.7 ± 0.2 | 1.9 ± 0.2 | $4.3 \pm 0.3$ | 1.1 ± 0.2 | 2.3 ± 0.25 |  |  |

#### SERIES LIST

|     |                 | L     | RI   | C     | Is   | at   | Irr      | ns        |

|-----|-----------------|-------|------|-------|------|------|----------|-----------|

| No. | Part No.        | (µH)  | (m   | ιΩ)   | (/   | 4)   | (A)      | Тур.      |

|     |                 | ± 20% | Тур. | Max.  | Тур. | Max. | 20℃ rise | 40°C rise |

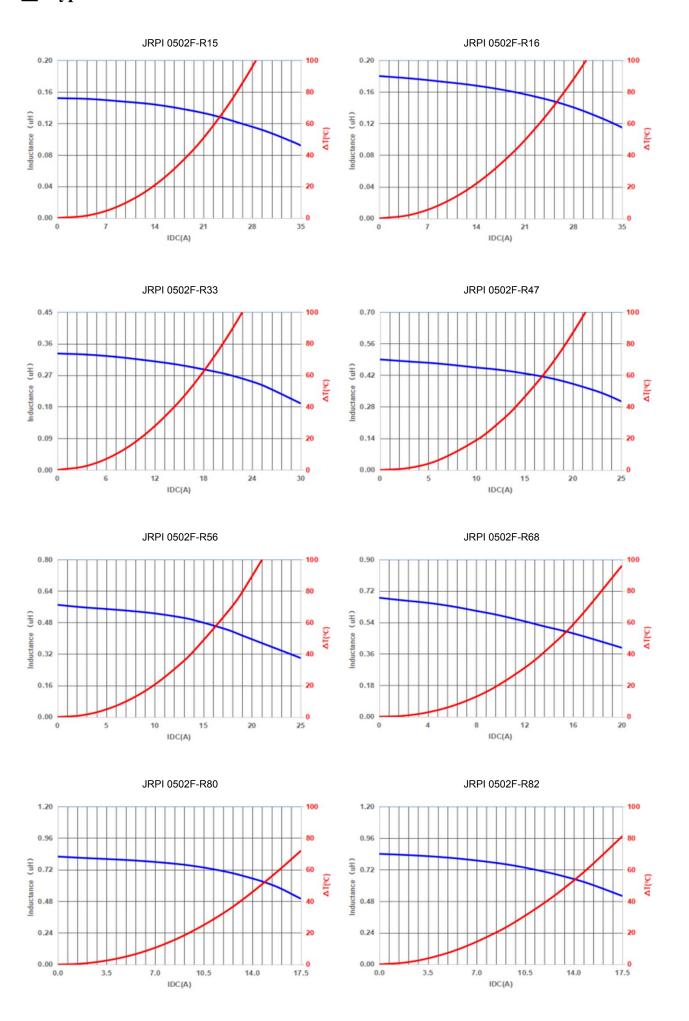

| 1   | JPRI 0502F-R15M | 0.15  | 4.00 | 4.60  | 30.0 | 27.0 | 13.9     | 18.8      |

| 2   | JPRI 0502F-R16M | 0.16  | 4.00 | 4.60  | 30.0 | 27.0 | 13.9     | 18.8      |

| 3   | JPRI 0502F-R33M | 0.33  | 6.10 | 7.00  | 26.0 | 24.0 | 10.5     | 14.4      |

| 4   | JPRI 0502F-R47M | 0.47  | 7.00 | 8.05  | 22.0 | 20.0 | 10.1     | 14.1      |

| 5   | JPRI 0502F-R56M | 0.56  | 8.70 | 9.54  | 19.0 | 16.0 | 9.9      | 13.9      |

| 6   | JPRI 0502F-R68M | 0.68  | 8.90 | 10.20 | 16.0 | 14.0 | 9.6      | 13.4      |

| 7   | JPRI 0502F-R80M | 0.80  | 10.3 | 11.80 | 15.5 | 13.5 | 9.4      | 13.0      |

| 8   | JPRI 0502F-R82M | 0.82  | 11.0 | 12.70 | 15.0 | 13.0 | 8.5      | 12.0      |

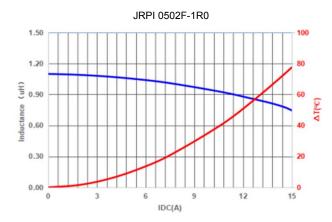

| 9   | JPRI 0502F-1R0M | 1.00  | 12.0 | 13.80 | 14.5 | 12.8 | 7.5      | 10.5      |

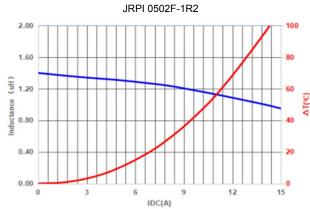

| 10  | JPRI 0502F-1R2M | 1.20  | 14.2 | 16.30 | 14.0 | 12.2 | 6.8      | 9.4       |

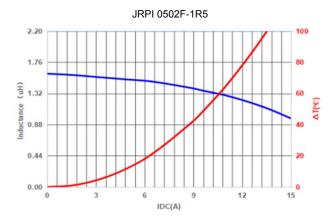

| 11  | JPRI 0502F-1R5M | 1.50  | 16.2 | 18.70 | 13.3 | 11.7 | 6.4      | 8.8       |

#### Note:

- 1. Test Frequency: 100KHz /0.1V

- 2. All test data referenced to 25°C ambient

- 3. Current that causes the specified temperature rise from 25°C ambient.

- 4. Saturation Current (Isat) will cause L0 to drop approximately 30%.

- 5. The part temperature (ambient + temp rise) should not exceed 125°C under worst case operating conditions. Circuit design,component,PCB trace size and thickness,airflow and other cooling provisions all affect the part temperature. Part temperature should be verified in the end application.

- 6. Irms Testing: Temperature rise is highly dependent on many factors including pcb land pattern, trace size, and proximity to other components. Therefore temperature rise should be verified in application conditions.

- 7. Rated voltage 40V DC , The application of voltage depends on many factors , Over voltage may cause components failure , high temperature , and burn-out , User needs to verify for appropriate usage.

- 8. Rated DC current: The lower value of Irms and Isat.

#### Materials

| NO | Items  | Materials                    |

|----|--------|------------------------------|

| 1  | Core   | Alloy Powder                 |

| 2  | Wire   | Polyester Wire or equivalent |

| 3  | Solder | 100% Pb free solder          |

| 4  | Ink    | Halogen-free ketone          |

## **■** Typical Performance Curves

## Appearance criterion

## 1 . PAD residual powder . inner wire exposed . imprinting

The residual powder on both side of pad is norm and within following criteria are acceptable

| а | 10% max of the length of pad.         | a      | 1 |

|---|---------------------------------------|--------|---|

| b | 5% Max of the area on one single pad. | Note 1 |   |

| t | 0.08mm max.                           |        |   |

|   |                                       | Note 2 |   |

#### Note:

- 1 · The imprinting mark below the part, are norm in manufacturing process and does not affect the function and it is acceptable.

- 2 · Residual powder on the product body is inevitable and accepted.

### 2 · Chip

Chip off is generated during molding and manufacturing process.

Chip off acceptance limits subjected to the product size.

Our current Defect limit is based on the IPC-A-610-2017standard of Method 9.4.

Some chip off does not impact the product function, see the IPC standard 1 & 2.

| Т | 25 % Max of the thickness |

|---|---------------------------|

| W | 25 % Max of the width     |

| L | 50 % Max of the length    |

Defects usually occur at the corners and edges of the product, There will be a slight defect black and rough, but not exposed copper, and does not affect the product performance and reliability.

Each considered separately

#### 3 · Crack

Production process of cracks appearing in the body is inevitable, some slight crack is caused because the molding, is not oxidized, crack on the product will not affect product performance.

We have done a reliability test of crack products, even if cracks is more than 0.2mm width also will not affect the electrical properties of the product, crack limits as follows (Length  $\leq$  1/3 body, width  $\leq$  0.2mm---OK) :

Severely crack: not acceptable More obvious cracks extended from side to side

Moderate crack: not acceptable Very obvious and may result in powder come off and exposed of copper wire

Slight wire expose: acceptable wire exposed during Press process

Lead wire imprint: acceptable Turns of wires that close to the edge and imprint show

Slight crack: acceptable

Products from a slight crack in the baking process due to thermal expansion, and it is not obvious by visual inspection (Must not exceed the blue square area)

#### 4 · oxidation(rust)

The contains iron composite, although the resin has a protective effect of oxidation, but there will be small amount of product that may occur oxidation.it is recommend that customer use this product in humidity controlled environment. The basic steps should be to protect the surface oxidation, including the sealed packages to PCB mount inductors. To avoid the adverse effects caused by oxidation, Oxidation occurs at the surface only allows the internal oxidation is not allowed, oxidized surface will not affect the reliability of the product.

4sides slightly oxidized side: Acceptable

Top and bottom slightly oxidized side: Acceptable

Spray printing effect : can be accepted if recognizable

Oxidation (rust) area refer to Standard Chip 2

Ps: Visual Condition: visual inspection

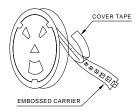

## **Packaging Information**

## • Reel Dimension

| Туре     | A(mm)     | B(mm) | C(mm)       | D(mm) |

|----------|-----------|-------|-------------|-------|

| 13"x12mm | 12.4+2/-0 | 100±2 | 13+0.5/-0.2 | 330   |

## • Tape Dimension

| Ao(mm)  | Bo(mm)  | Ko(mm)  | P(mm)   | W(mm)    | F(mm)   | T(mm)     | D(mm)   |

|---------|---------|---------|---------|----------|---------|-----------|---------|

| 6.4±0.1 | 6.1±0.1 | 2.3±0.1 | 8.0±0.1 | 12.0±0.3 | 5.5±0.1 | 0.35±0.05 | 1.5±0.1 |

## • Packaging Quantity

| Size       | Reel |

|------------|------|

| JRPI 0502F | 3000 |

## • Tearing Off Force

Top cover tape

F 165° to180°

Base tape

The force for tearing off cover tape is 10 to 130 grams in the arrow direction under the following conditions (referenced ANSI/EIA-481-D-2008 of 4.11 standard)

| Tearing Speed | Room Temp. | Room Humidity | Room atm |

|---------------|------------|---------------|----------|

| mm            | (℃)        | (%)           | (hPa)    |

| 300±10%       | 5~35       | 45~85         | 860~1060 |

## Application Notice

Storage Conditions(component level)

To maintain the solderability of terminal electrodes:

- 1. Products meet IPC/JEDEC J-STD-020E standard-MSL, level 1.

- 2. Temperature and humidity conditions: Less than  $40\,^\circ\!\!\!\!\mathrm{C}$  and 60% RH.

- 3. Recommended products should be used within 12 months form the time of delivery.

- 4. The packaging material should be kept where no chlorine or sulfur exists in the air.

- Transportation

- 1. Products should be handled with care to avoid damage or contamination from perspiration and skin oils.

- 2. The use of tweezers or vacuum pick up is strongly recommended for individual components.

- 3. Bulk handling should ensure that abrasion and mechanical shock are minimized.